編者按:隨著芯片制造工藝來到了2nm后,GAA晶體管開始逐漸進入主流。到翻看這個技術的發展,最早在2006年就有相關研究發布。當中論文的參與者還有一個華人。

在本文中,我們回顧一下20年前是如何看待這個晶體管的。

早期研究展示了下一代晶體管設計的新方法

隨著微電子行業開始在下一代智能手機中采用環柵晶體管設計,勞倫斯伯克利國家實驗室(伯克利實驗室)近 20 年前的開創性研究展示了一種創建這些先進結構的創新方法。

這項名為“環柵場效應晶體管”(GAA-FET)的技術代表著一項關鍵的架構進步,有望將數十億個晶體管封裝到智能手機和筆記本電腦的微型芯片中。“環柵”設計增強了對晶體管溝道的控制,從而提高了性能并降低了功耗。雖然目前業界仍在通過傳統的自上而下的制造方式來實現GAA-FET,但伯克利實驗室早期的自下而上方法展示了這種幾何結構利用化學合成實現這些復雜結構的潛力。

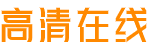

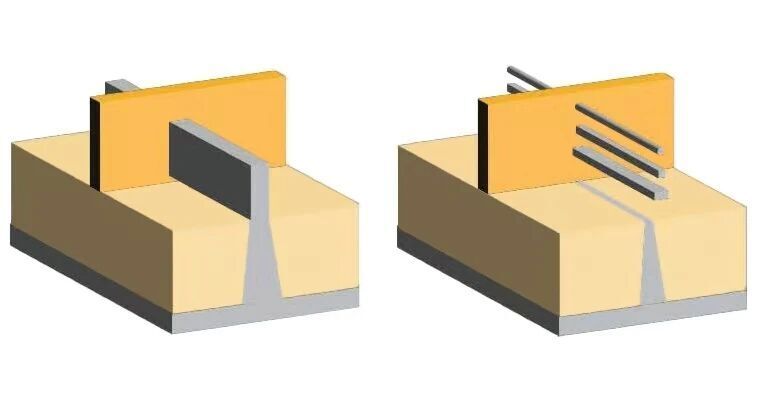

圖示:在環柵 (GAA) 結構(右圖)中,柵極環繞納米級硅通道的四邊,納米級硅通道以三條灰色納米線與黃金矩形相交的形式呈現。這些通道是電流的通道。在鰭式場效應晶體管 (FinFET) 結構(左圖)中,柵極僅覆蓋矩形通道(灰色)的三條邊。GAA 結構可以更精確地控制電流。

“我很高興看到半導體行業晶體管架構的持續發展,”楊培東(Peidong Yang,江蘇蘇州人)說道。他在2006年的一篇開創性論文中發表了關于自下而上合成環繞柵極結構的研究成果。“我們早期對化學合成方法創建復雜晶體管幾何結構的探索,展示了制造這些結構的替代途徑。”楊培東是伯克利實驗室材料科學部的資深科學家,也是加州大學伯克利分校化學和材料科學與工程系的教授。

晶體管是現代計算的基本組成部分——如今智能手機中一些性能最佳的微芯片由超過100億個晶體管組成,每個晶體管的尺寸僅為5納米。每個晶體管就像一個開關,允許或阻止電流通過半導體通道,從而實現支撐現代計算的二進制運算。

晶體管的柵極是決定晶體管導通或截止的控制輸入。過去十年,最常見的晶體管設計是鰭式場效應晶體管 (FinFET),它將半導體通道垂直放置,就像微型沖浪板上的鰭片,柵極從三面環繞通道。然而,將 FinFET 縮小到 5 納米以下會降低柵極效率和能效。

微芯片制造商希望通過將數百億個晶體管封裝到指甲蓋大小的芯片中,繼續突破摩爾定律的極限。更高的晶體管密度需要更小的晶體管——小到2納米(DNA鏈的大小),或者更大膽地說,小到幾個硅原子的大小(1納米)。更小的芯片意味著更小的設備,同時也能提高芯片的能效。

幾十年來,微電子行業一直都知道,環繞柵極(GAA)方法(一種將柵極完全包裹溝道的設計理念)有可能在 5 納米以下的尺度上制造出性能更高、效率更高的晶體管。盡管傳統的自上而下光刻技術在 21 世紀初制造 GAA-FET 幾何結構時面臨技術挑戰,但研究人員仍在探索各種方法和結構來實現這一設計理念。

楊的團隊首次展示了一種非傳統的自下而上方法,利用化學氣相沉積 (CVD) 技術制造硅基環柵晶體管。在他們2006年發表于《納米快報》的開創性論文《Silicon Vertically Integrated Nanowire Field Effect Transistors》中,楊的團隊利用CVD技術生長出垂直硅納米線,納米線表面覆有超薄金屬層,并嵌入二氧化硅中。他們利用行業標準材料,通過化學合成而非傳統光刻技術,實現了環柵結構。